- Title

- Hyeonho han (Prof. Chae’s research team) published in the IEEE Journal of Solid-State Circuit (JSSC)

- Date

- 2024.01.17

- Writer

- 전기전자공학부

- 게시글 내용

-

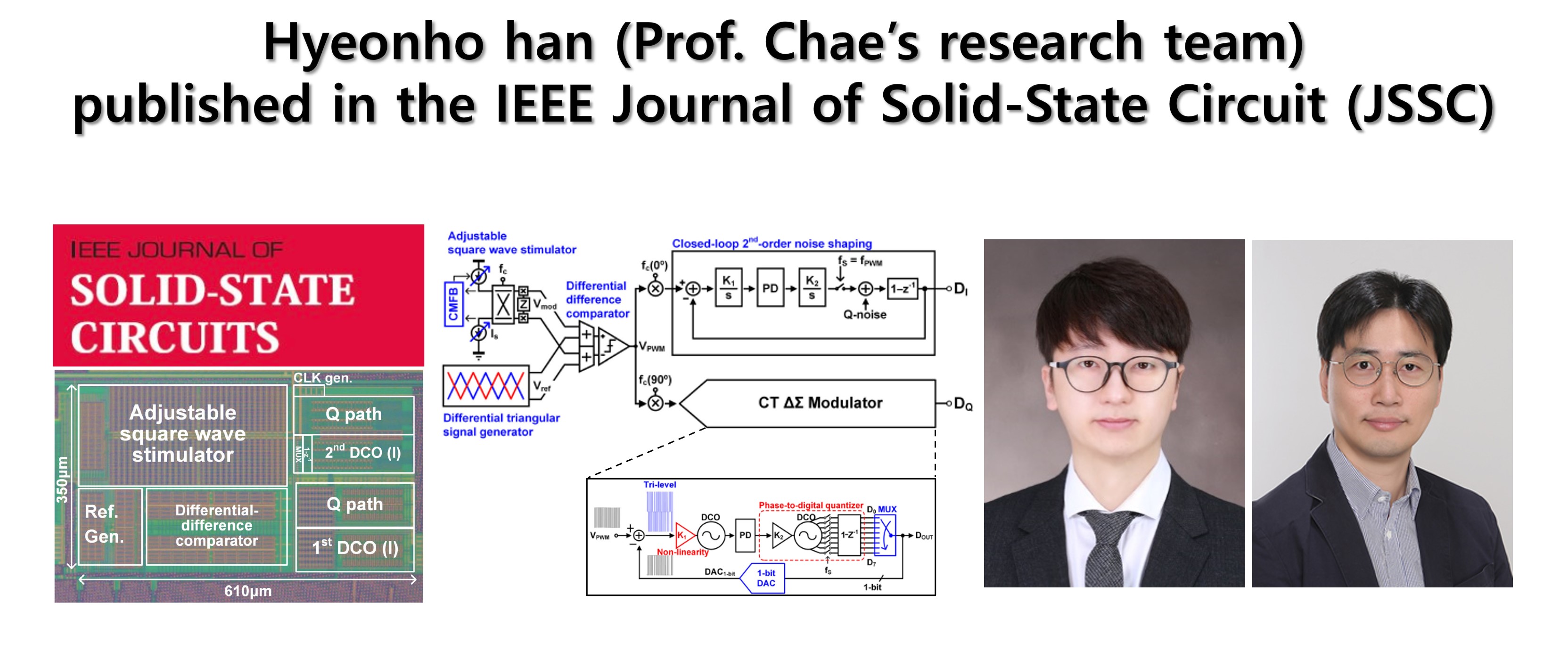

Prof. Chae’s research team has published the paper titled “A Highly Digital 143.2-dB DR Sub-1◦ Phase Error Impedance Monitoring IC With Pulsewidth Modulation Frontend” in the IEEE Journal of Solid-State Circuits (JSSC), which is a leading academic journal in the field of circuit and system (IF 5.4). This research paper demonstrates innovative findings that using PWM for sensor interface yields improved area, power, and phase error performance.

This work was supervised under Prof. Youngcheol Chae (Corresponding author) and led by graduate student Hyeonho Han (first author).

- Attachments

- temp.jpg