- 제목

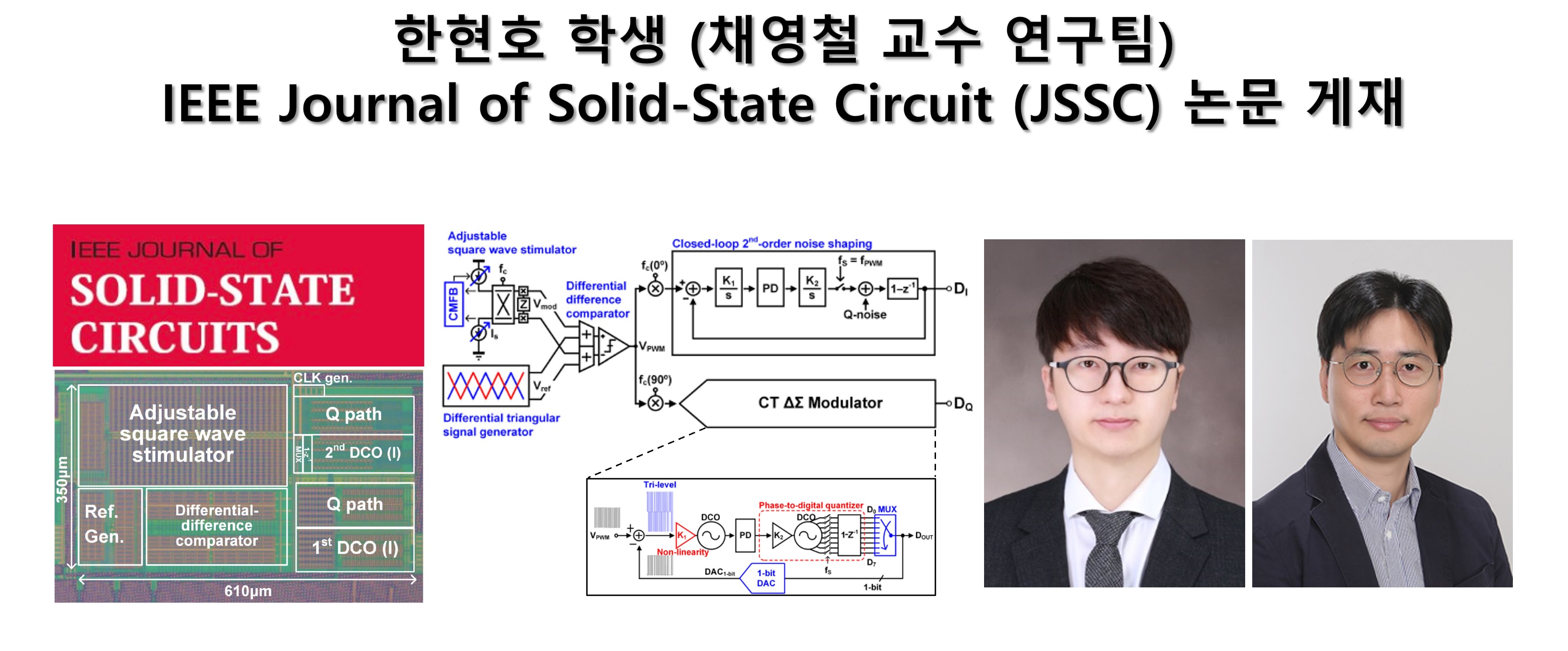

- 한현호 학생 (채영철 교수 연구팀) IEEE Journal of Solid-State Circuit (JSSC) 논문 게재

- 작성일

- 2024.01.17

- 작성자

- 전기전자공학부

- 게시글 내용

-

채영철 교수 연구팀은 “A Highly Digital 143.2-dB DR Sub-1◦ Phase Error Impedance Monitoring IC With Pulsewidth Modulation Frontend” 논문을 회로 및 시스템 분야의 최고 학술지인 IEEE Journal of Solid-State Circuits (JSSC) (Impact Factor 5.4)에 게재하였다. 해당 연구논문은 PWM을 활용하여 센서 인터페이스를 만들면 면적, 파워, 페이즈 에러 성능이 좋다는 것을 증명한 혁신적인 연구결과이다.

본 연구는 채영철 교수(교신저자)가 지도하고, 제1저자인 한현호 학생이 주도하였다.

- 첨부

- temp.jpg